Intel’s new Z-Angle Memory (ZAM) project is starting to move from “interesting research” to something that looks far more real. After gaining noticeable attention in recent weeks, Intel and its partners have now shown an early prototype of the technology and are making big promises about how it could tackle the growing thermal and performance limits seen in today’s high-bandwidth memory solutions.

Intel has been out of the traditional DRAM business for decades, which makes this development especially notable. Instead of returning to conventional memory, the company is backing a fresh approach alongside Saimemory, a SoftBank subsidiary, with the goal of challenging the current dominance of HBM in AI and high-performance computing.

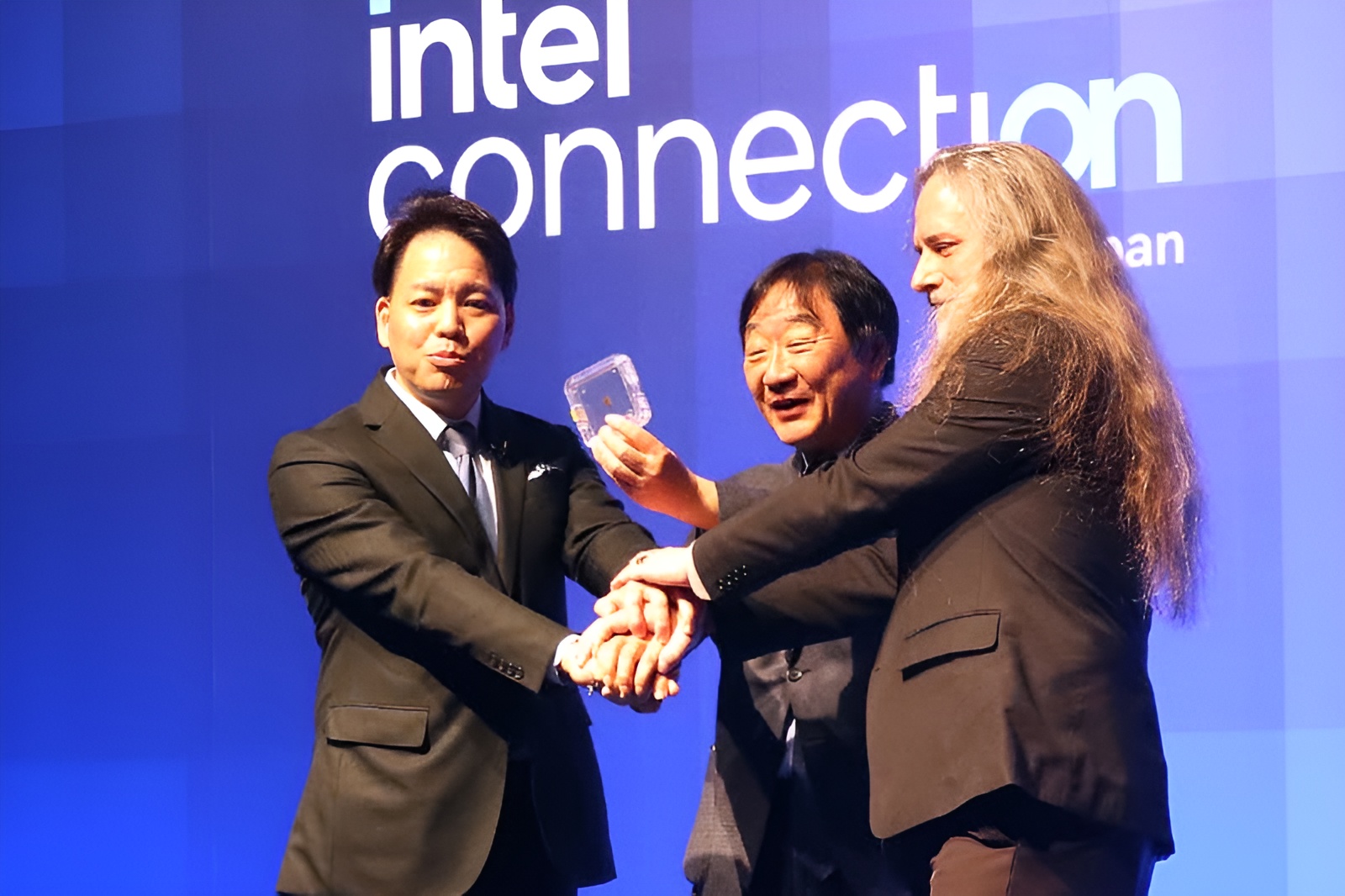

The first official public overview of ZAM was presented at the Intel Connection Japan 2026 event. Intel Fellow and CTO of Intel Government Technologies Joshua Fryman appeared at the event alongside Intel Japan CEO Makoto Onho, signaling that this isn’t just a quiet experiment. Until now, ZAM discussion was mostly limited to papers and formal announcements, but the appearance of a prototype suggests the project is advancing into a more tangible phase.

So what makes Z-Angle Memory different? The key idea is in the way stacked memory layers connect to each other. Traditional stacked memory designs typically rely on vertical connections that go straight down through the stack. ZAM uses a staggered “diagonal” interconnect topology instead—routing connections at an angle through the die stack rather than drilling directly downward. Intel’s message is that this architectural change can improve how heat is handled inside dense memory stacks, which is becoming a major bottleneck as workloads and bandwidth demands climb.

While Intel hasn’t fully detailed every part of its role, the materials shared at the event point to Intel being responsible for initial investment and higher-level strategic decisions. In other words, Intel appears positioned as a key backer shaping the direction of the project rather than simply observing from the sidelines.

Early expectations being discussed around ZAM include several potential advantages that would matter directly to data centers and AI hardware designers: claims of 40–50% lower power consumption, easier manufacturing enabled by Z-angle interconnects, and much higher capacity per chip—reportedly up to 512 GB. If even part of that roadmap proves achievable at scale, ZAM could become a serious alternative for companies struggling with the power and thermal challenges that come with pushing HBM further.

For now, Z-Angle Memory remains in the prototype stage, but Intel’s decision to publicly showcase it—and to do so with high-profile executives present—strongly suggests the company sees a real opening in the fast-growing memory market tied to AI accelerators and high-performance computing. As the industry searches for better ways to balance bandwidth, heat, and energy use, ZAM is shaping up to be one of the more intriguing technologies to watch.