For years, Apple and NVIDIA have largely stayed in their own lanes inside TSMC’s vast manufacturing ecosystem. Apple has relied on TSMC’s most advanced process nodes and InFO (Integrated Fan-Out) packaging to power its A-series iPhone chips and M-series Mac processors. NVIDIA, on the other hand, has typically paired TSMC production with CoWoS (Chip-on-Wafer-on-Substrate) advanced packaging to build the GPU powerhouses that drive modern AI.

That clean separation is starting to blur, and it could set up a high-stakes fight for TSMC’s most valuable resource right now: advanced 3D packaging capacity. As Apple pushes toward more complex, multi-die designs and more ambitious performance targets, it’s heading into the same packaging territory that NVIDIA already dominates. The result could be a capacity crunch with real-world consequences for product timelines, chip supply, and even where Apple chooses to manufacture future silicon.

Apple’s packaging strategy is rapidly evolving

Apple has traditionally used InFO-PoP packaging for many of its chips, a technique where DRAM is mounted directly on top of the system-on-chip for compact designs and tight integration. But the next chapters of Apple silicon look far more modular.

For its upcoming A20 chips, Apple is expected to adopt WMCM packaging. This shift matters because WMCM enables multiple individual dies—such as CPU, GPU, and Neural Engine blocks—to be integrated into a single package. Instead of being locked into one monolithic design, Apple can mix and match die configurations, creating more flexibility across product tiers while potentially improving yields and scaling options.

At the same time, Apple is also expected to use TSMC’s SoIC-MH packaging for future M5 Pro and M5 Max chips. SoIC is a 3D packaging technology designed to stack chips both horizontally and vertically, delivering denser integration and higher bandwidth in less space. It’s the kind of approach that supports the next wave of high-performance computing designs—exactly where Apple wants its Mac and pro-grade silicon to go.

Clues are also emerging that Apple may eventually embrace CoWoS for higher-end M-series chips. One notable sign: upcoming M5-series chips are expected to use a new Liquid Molding Compound (LMC) supplied exclusively by Taiwan’s Eternal Materials. This material is engineered to meet the specifications required for CoWoS packaging, adding weight to the idea that Apple’s future roadmap aligns with the same advanced packaging methods that NVIDIA depends on.

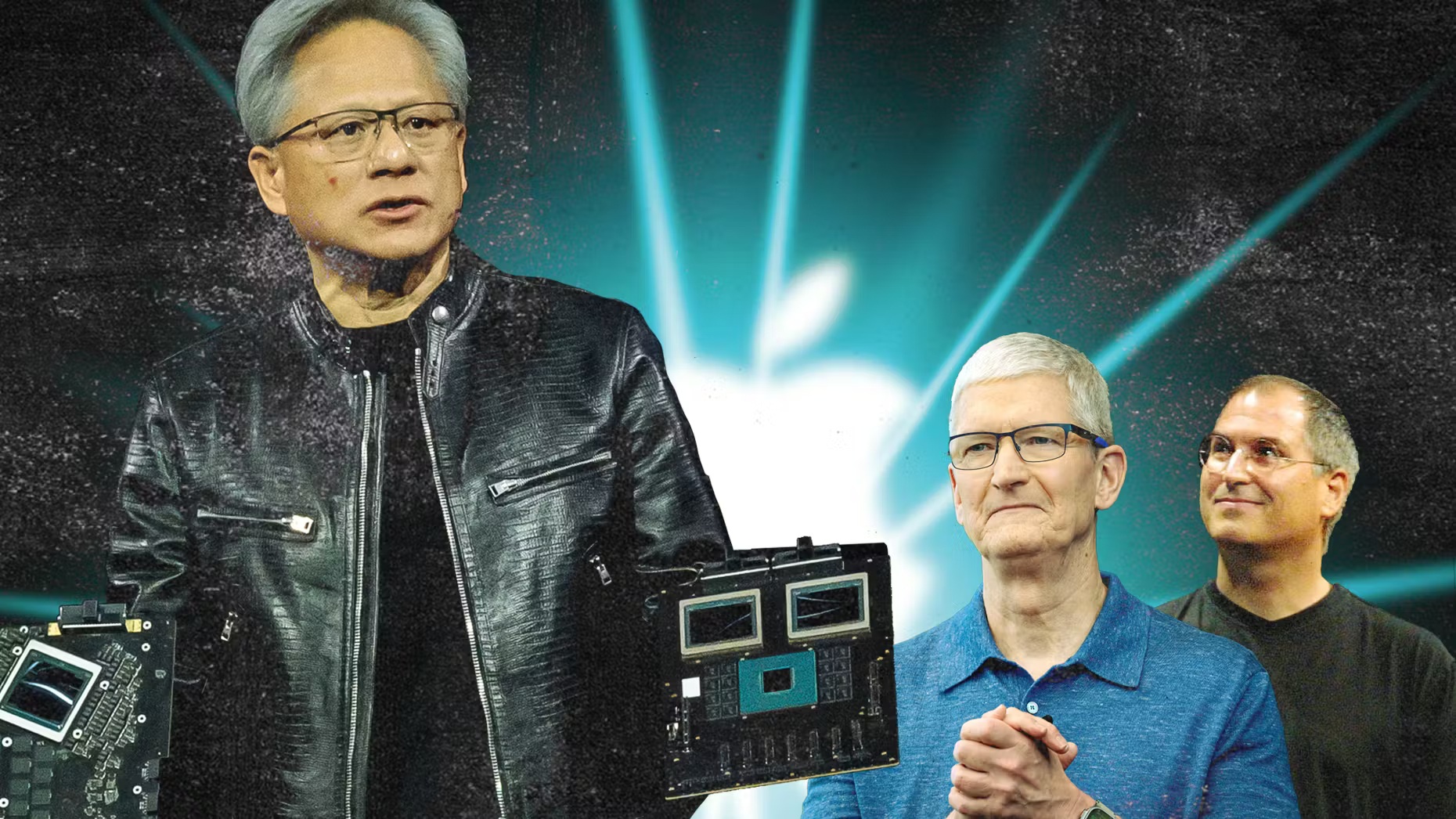

A looming collision at TSMC: Apple vs. NVIDIA

The core issue isn’t just process technology—it’s packaging capacity. Apple is heavily associated with TSMC’s InFO packaging lines, while NVIDIA is a major force in CoWoS-related capacity. As Apple moves toward higher-end chips like a future M5 Ultra or M6 Ultra using SoIC and WMCM-style approaches, both companies may end up competing for the same advanced 3D packaging resources across TSMC’s most in-demand packaging options.

This kind of convergence is more than an industry footnote. Advanced packaging has become one of the biggest bottlenecks in chip production, especially in the AI era where high-bandwidth memory integration and complex multi-die assemblies are essential. Even if wafer supply is available, packaging constraints can slow the entire pipeline.

TSMC has already been leaning on outside partners, handing off portions of advanced packaging volume to OSAT providers such as ASE and Amkor. That helps relieve some pressure, but it also highlights how stretched advanced packaging capacity has become as demand accelerates.

Why Intel and Samsung could benefit

If Apple and NVIDIA are forced into a direct contest for TSMC’s premium packaging slots, Apple may have a strong incentive to diversify more of its chip production. That could mean shifting part of its fabrication and packaging needs to alternative foundry partners such as Intel and Samsung, especially for lower-end chips where Apple has more flexibility in scheduling and volume planning.

In fact, Apple is already evaluating Intel’s 18A-P process for lower-tier M-series chips expected to arrive around 2027. Estimates suggest that if Apple moved roughly 20 percent of its base M-series wafer volume to Intel’s 18A-P, it could translate into substantial foundry revenue for Intel—potentially hundreds of millions of dollars—depending on wafer pricing, die size, and yield levels.

The bigger takeaway is simple: TSMC’s advanced packaging has become just as strategic as its leading-edge nodes. As Apple’s chip designs become more modular and more 3D-focused, it’s drifting into the same packaging battlefield that fuels NVIDIA’s AI dominance. If TSMC can’t expand advanced packaging capacity quickly enough, the ripple effects could reshape supply chains—and open the door wider for Intel and Samsung to win meaningful Apple silicon business in the years ahead.