Zhaoxin has officially launched its KH-50000 server CPUs, signaling a major leap for China’s domestic data center ecosystem. Built around a chiplet-based architecture and scaling up to 96 cores per socket, the new lineup focuses on higher compute density, faster I/O, and improved efficiency—exactly what modern cloud, virtualization, and data analytics workloads demand.

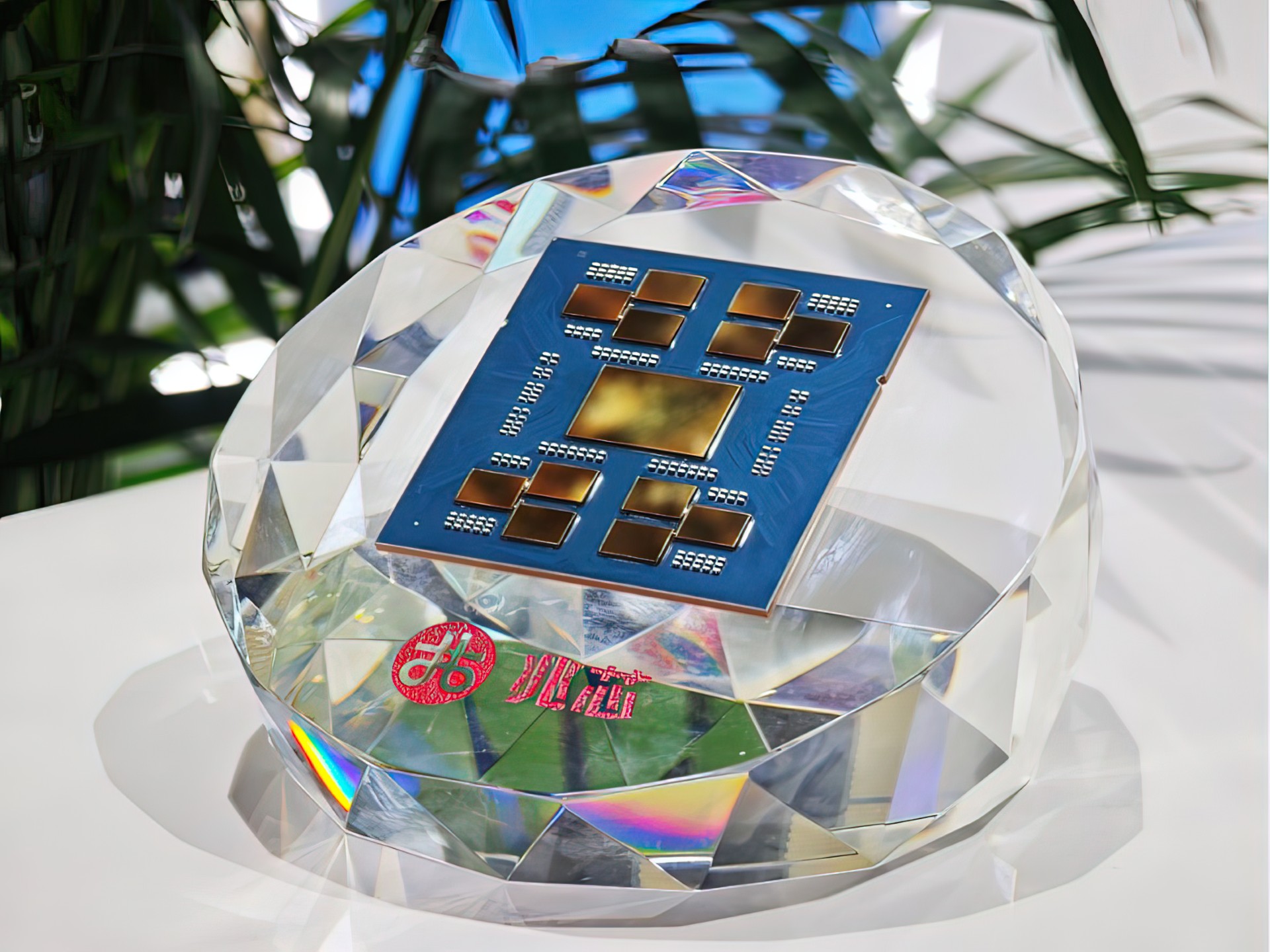

At the heart of the KH-50000 is an advanced multi-chip module that integrates 12 compute chiplets alongside a large I/O die. The design is paired with the new ZPI 5.0 interconnect, enabling both dual-socket and quad-socket configurations. That means a single 4P server can host up to 384 cores, while enjoying higher bandwidth and lower latency with better power characteristics compared to the previous generation.

Key performance and architecture highlights:

– Up to 96 cores per CPU

– 2.0 GHz base and 3.0 GHz boost clock speeds

– Up to 384 MB of cache

– Around 30% IPC improvement over the last architecture

– SMT support has not been confirmed

Memory and connectivity get a substantial upgrade. KH-50000 adds 12-channel DDR5 ECC memory support for big boosts in throughput and capacity. On the expansion side, there are 128 lanes of PCIe 5.0 with ZPI/CXL compliance for high-speed accelerators, storage, and networking, plus 16 additional lanes that can serve PCIe 4.0, SATA, and USB connectivity. The overall package and heat spreader design bear similarities to widely known high-core-count server CPUs, continuing a trend seen in Zhaoxin’s previous generations.

How KH-50000 compares to KH-40000:

– 96 cores vs 32 cores

– 3.0 GHz peak vs 2.5 GHz peak

– 384 MB cache vs 64 MB cache

– 12-channel DDR5 vs 8-channel DDR4

– 128 PCIe 5.0 lanes vs 128 PCIe 4.0 lanes

– ZPI 5.0 interconnect vs ZPI 3.0

For domestic data centers, the KH-50000 family represents a sizable step forward in compute density, memory bandwidth, and platform scalability. The combination of 12-channel DDR5 and 128 PCIe 5.0 lanes makes it suitable for high-I/O environments, from NVMe-heavy storage nodes to GPU- or accelerator-rich AI and HPC clusters.

Zhaoxin is also pushing on the client side. The newly announced KX-7000N is an evolution of the KX-7000, now integrating a dedicated NPU to accelerate AI workloads on consumer systems. Looking ahead, there are indications of a next-generation KX series aimed at the AI PC segment, promising more CPU cores, stronger overall compute, PCIe 5.0 support, and a new high-performance heterogeneous NPU architecture.

With KH-50000 entering the market and consumer chips adding on-device AI acceleration, Zhaoxin is expanding its footprint across servers and PCs. Expect more updates as the company continues to iterate on performance, efficiency, and platform capabilities in the coming quarters.