The race to deliver more compute isn’t just about smaller transistors anymore. As AI, data center, and high-performance workloads explode, chipmakers are leaning hard on advanced packaging to stitch multiple dies together into a single, high-performance system. That space has long been associated with one dominant supplier, but momentum is shifting. Intel’s EMIB and Foveros technologies are drawing fresh interest from top-tier companies, signaling a broader realignment in the semiconductor supply chain.

Recent job listings offer a telling glimpse into what’s coming next. Apple is hiring for roles that call out experience with advanced packaging, specifically naming EMIB alongside technologies such as CoWoS, SoIC, and PoP. Qualcomm is also seeking leadership with familiarity in EMIB for its data center business. While job postings aren’t formal product commitments, they’re a strong indicator that industry heavyweights are actively evaluating Intel’s packaging toolkit.

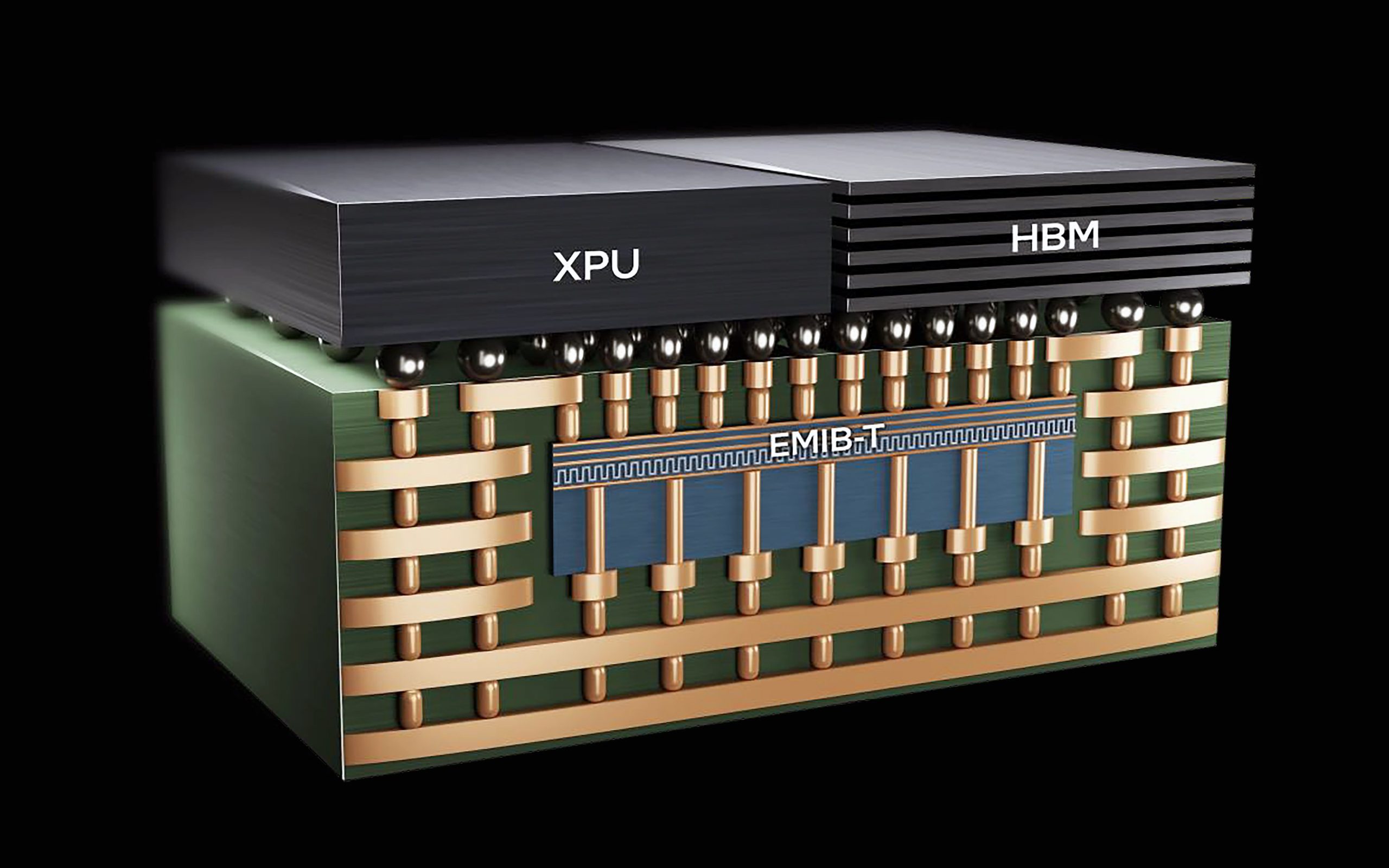

At the heart of the buzz are two complementary approaches from Intel. EMIB, short for Embedded Multi-Die Interconnect Bridge, enables high-density connections between chiplets using tiny silicon bridges embedded in the package substrate. This sidesteps the need for the large full-size interposers typical of some 2.5D solutions, which can simplify design and help with cost and scalability as chiplets proliferate.

On top of that, Foveros brings true 3D stacking into play. By vertically integrating dies with through-silicon vias, Intel can stack compute, memory, or I/O on a base die, shrinking data paths and enabling new performance-per-watt profiles. The newer Foveros Direct approach pushes toward even denser and lower-resistance interconnects. Across the industry, Foveros is widely regarded as a leading-edge option for heterogeneous integration.

The timing favors alternatives. Demand for advanced packaging has surged faster than capacity, with AI accelerators and HPC platforms consuming a massive share of available throughput. Companies already in volume with leading-edge GPUs and CPUs have locked in significant packaging capacity, creating bottlenecks that can push newer projects down the queue. That dynamic makes diversification attractive, and it’s exactly where Intel can step in with competitive offerings and expanding capacity.

For companies building custom silicon—think Apple, Qualcomm, and network silicon vendors like Broadcom—broadening packaging options can reduce risk, improve time-to-market, and provide leverage across foundry ecosystems. A DRAM packaging-focused role, for instance, hints at designs tightly coupling memory with compute, where both 2.5D and 3D approaches can be pivotal for bandwidth and latency targets.

Industry sentiment adds weight to the trend. NVIDIA’s leadership has publicly expressed appreciation for Intel’s 3D packaging progress, reinforcing the perception that Intel’s stack is ready for prime time in complex, multi-die systems. It’s not a confirmation of adoption, but it is a signal that the technology is earning respect at the highest levels.

What this means for the next wave of chips is straightforward: as AI models scale and data movement becomes the real bottleneck, the value shifts to how cleverly and efficiently dies are connected. EMIB’s fine-pitch, bridge-based links and Foveros’ vertical stacking are tailor-made for the chiplet era, where mixing process nodes, IP blocks, and memory types inside one package is becoming standard practice.

To be clear, job listings alone don’t equal a design win. But the growing number of roles citing EMIB and 3D packaging expertise suggests that engineering teams are actively qualifying multiple paths forward. With ongoing supply constraints in advanced packaging and intensifying demand from AI and HPC, Intel’s portfolio looks well positioned to capture meaningful share.

Bottom line: the center of gravity in semiconductors is moving from transistor scaling to system-level integration. Intel’s EMIB and Foveros are emerging as credible, timely alternatives for companies that want leading performance without being bottlenecked by a single packaging pipeline. If interest translates into adoption, expect the next generation of compute engines—from mobile to data center—to lean heavily on Intel’s advanced packaging to hit their performance, power, and schedule targets.